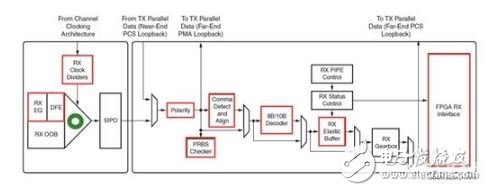

The previous blog post introduced the GTX transmitter. This article will introduce the GTX RX receiver. The structure of the GTX RX receiver is similar to that of the TX transmitter. The data flow direction is opposite, but there are some differences between the transmitter and the GTX. The end structure diagram is shown in Figure 1:

figure 1

The function of each circuit part of the RX receiving end will be introduced according to the direction of the data flow.

RX Equalizer (DFE and LPM): After the RX signal comes in from the AFE (Analog Front End), it first passes through the RX equalizer. The main function of the equalizer is to compensate for the high frequency loss of the signal during channel transmission because the channel is bandwidth dependent. Limited, so the signal will cause attenuation or even damage through it.

There are two types of equalizers on the RX receiver, LPM and DFE. The power consumption and performance are different. The LPM consumes less power. The DFE can provide more accurate filter parameters, which can better compensate the transmission channel. Loss, so performance is better.

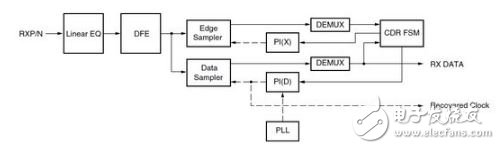

RX CDR: The clock data recovery circuit of RX is the green circle part of Figure 1. Because the GTX transmission does not have the associated clock, the clock recovery and data recovery must be done at the receiving end. The clock data recovery circuit is shown in Figure 2:

figure 2

The specific process is shown in Figure 2. First, the external data comes in and passes through the equalizer, and then the data from the equalizer enters the clock data recovery circuit. GTX uses a phase-rotating CDR structure, and the data coming in from the DFE is captured by the edge sampler and the data sampler, respectively, and then the CDR state machine determines the phase of the data stream according to the two and feedbacks the phase interpolator (PI), when the data sampler The edge sampler is locked to the transmission domain of the data stream when the location is in the center of the eye. The CPLL or QPLL provides the basic clock for the phase interpolator, which enables the CDR state machine to perform phase control well.

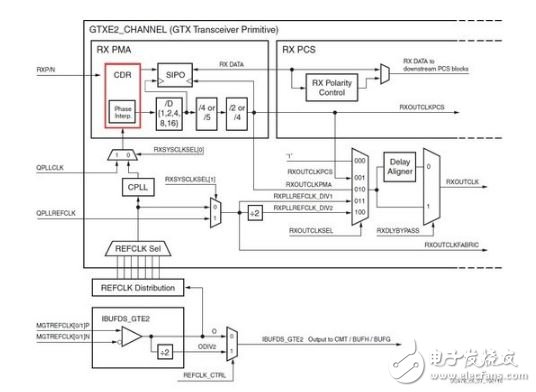

RX Fabric Clock Output Control: The clock structure of the RX receiver is very similar to that of the TX transmitter. As shown in Figure 3, the CDR portion of the red box in the figure is the biggest difference from the TX terminal.

image 3

Like the TX transmitter, the clock structure of the RX receiver is also mainly divided into a serial clock divider and a parallel clock divider. The D divider is a serial clock divider to reduce the PLL clock rate to support lower The line rate, followed by the clock divider is mainly based on the set bit width and whether to use 8b/10b to generate different parallel data clocks.

RX Polarity Control: Like the TX transmitter, the RX receiver also has polarity control, which can be used to implement data flipping. This function is used when RXP and RXN are connected in reverse during PCB design.

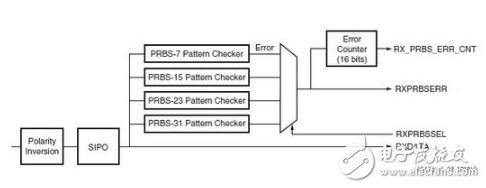

RX Pattern Checker: GTX includes an embedded PRBS checker. As shown in Figure 4, there are four different pseudo-random sequence generators to choose from. The checker is self-synchronizing and works before boundary alignment and decoding. Features can be used to test signal integrity.

Figure 4

RX Byte and Word Alignment: Before the serial data is parallelized, for example, find a suitable feature boundary. This feature boundary or character boundary is an identifiable sequence sent by the TX sender, usually called a comma or K code, the receiving end searches for the identifier in the incoming data. When the identifier is found, the data received later is parallelized by the identifier. The working principle is shown in FIG. 5.

Figure 5

As shown in Figure 5, after the comma is searched for in the serial data (red box), the latter data is already border-aligned data.

RX 8B/10B Decoder: If the data sent by the sender is 8B/10B coded, then 8B/10B decoding is needed at the receiving end. Otherwise, it can be bypassed. This function is described in the TX sender. Here is the description. No longer introduce.

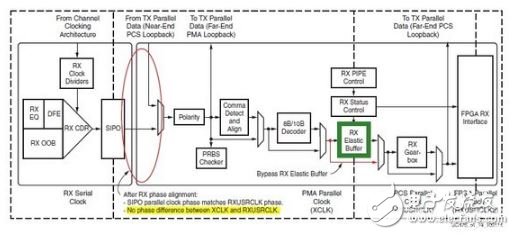

RX ElasTIc Buffer: The RX Receiver Elastic Buffer is an important feature. Compared to the TX Receiver Buffer, RX has an extra "elastic" attribute, meaning that the RX Elastic Buffer has more than the TX Transmitter. The function (RX clock correction and RX channel binding). The position of the RX elastic buffer at the RX receiving end is shown in the green box of Figure 6.

Figure 6

As can be seen from Figure 6, the RX receiver PCS sublayer has two main clock domains, the XCLK and RXUSRCLK clock domains. The RX elastic buffer function is mainly used to match the two clock phase differences.

If the RX elastic buffer is bypassed, in order to ensure stable reception of data, certain conditions must be met. First, a phase alignment circuit is required to process the phase difference between the SIPO circuit clock and the XCLK clock. Secondly, XCLK needs to be configured as a RXUSRCLK clock to ensure XCLK and RXUSRCLK have the same clock domain and there is no phase difference.

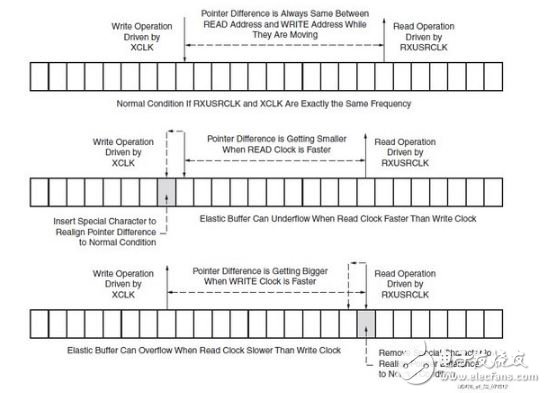

RX Clock CorrecTIon: The "elasticity" of the RX elastic buffer is reflected in the fact that the frequency difference between XCLK and RXUSRCLK can be adjusted by clock correction. For the RX receiver, even if XCLK and RXUSRCLK run at the same clock frequency, there are often some differences. This difference can easily cause the RX elastic buffer to be full or read, and the clock correction function comes into being. The clock correction function is shown in Figure 7.

Figure 7

Generally speaking, at the TX sender, we will periodically send K code to ensure the alignment of the receiving end boundary. When the data in the RX elastic buffer is insufficient, the received K code data will be copied and written into the RX elastic buffer. To keep the RX elastic buffer half full. When the RX elastic buffer data is too much, the received K code data will be discarded and not written to the RX elastic buffer to keep the RX elastic buffer half full.

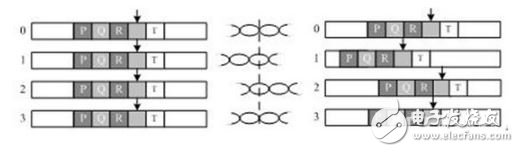

RX Channel Bonding: The channel bonding function also reflects the "elasticity" of the RX elastic buffer. For protocols like PCIE and SRIO, multiple lane transmissions can be supported to increase the total transmission bandwidth. Because of the transmission channel, the data sent by the TX sender at the same time cannot be received by the RX receiver at the same time. Each Lane receives the time difference, so it needs to be realigned when restoring data, so it needs to be received in RX. The channel performs the channel binding function.

In order to achieve this function, the TX sender adds a channel binding sequence to the transmitted data stream. The RX receiver adjusts the channel binding sequence detected by each lane in its respective RX elastic buffer. And delay, and finally make the data of each lane no offset, the output of the FPGA RX Interface can be the same as the data sent by the TX sender. The function is shown in Figure 8. The left side is unaligned data, and the right side is aligned data.

Figure 8

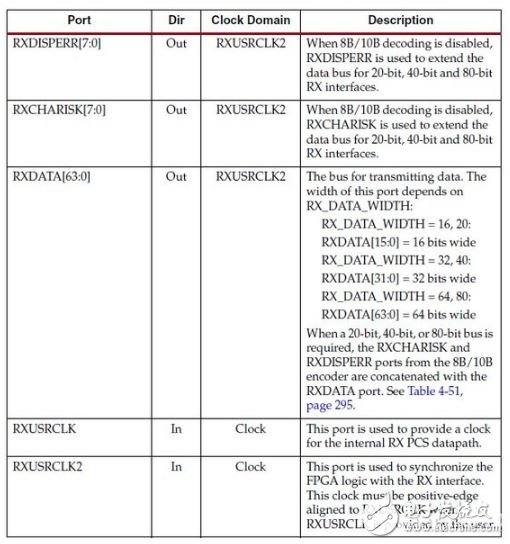

FPGA RX Interface: The user receives data through the FPGA RX Interface. Similar to the TX transmitter, it receives data on the rising edge of RXUSRCLK2 (the TX transmitter sends data on the rising edge of TXUSRCLK2). The user port can be set to 16/20/32/. 40/64/80bit bit width, the rate of RXUSRCLK2 is determined by the RX line rate, RXDATA bit width and 8B/10B enable. The specific ports are shown in Table 1, similar to TX, and will not be described.

Outdoor Front Service LED Display

Front Service Outdoor Fixed Install LED Display Screen

1. High refresh rate: With NOVA STAR control system, no scanning line when photographed

2. High gray level: 256 RGB each ,display 16.7M colors ,vivid and perfect video effect

3.High resolution: The most apparent features of the new generation of LED display

4.Good color uniformity

5. High Brightness: 6000-8000 cd/m2 ,brightness automatically adjusted

6. High Quality: CE, RoHs, FCC, UL, IP65, ISO9001 passed + 96 Hours serious testing time

7. Long life span: over100,000hours, warranty from 2 years.

* Nova MSD 300 sending card and Nova mrv328 receiving card

* Cabinet size:960x960mm

* Kinglight/Nationstar LED Lamp, Refresh rate:1920-3840hz

* Ultra-Light designing, less than 30kg/pcs

* High brightness up to 6500cd/sq.m, even in the sunlight conditions can see clear, but low power consumption to save the electric power cost.

* High debugging brightness and no damage to gray scale, achieving the debugging technology for nice image.

* Passed the TÃœV,FCC,ROHS,CE cetification.

Outdoor Front Service LED Display,P3.91 Outdoor Led Screen,Led Stage Screen

Guangzhou Chengwen Photoelectric Technology co.,ltd , https://www.cwledpanel.com