Based on the above analysis, we chose the CPCI bus as the data communication platform of the distributed system. CPCI bus technology is a combination of PCI bus technology and mature European card assembly technology. In terms of electrical, logic and software functions, it is fully compatible with the PCI standard and breaks through the limitation of the PCI standard 4 slots, compared to the VME bus The low price of the module has the advantages of openness, easy expansion, high density, etc., and at the same time achieves 99.999% high availability. Using CPCI bus technology and hardware interface design specifications, it can use its multi-module plug-in design advantages to support distributed processing of multiple services, and realize the seamless connection of modular data processing units, providing high-speed, Reliable guarantee, very suitable as a distributed system business processing communication platform, also suitable for a wide range of applications in communications and embedded systems [2-4].

This paper presents a design of a communication system based on the CPCI bus. The system uses a distributed network architecture to support the processing and data interaction of multiple packet switching services. The article first gives the system structure and principle design, and aims at the difficulties of the distributed business processing module cross-bus communication, proposes a message storage and address information maintenance strategy based on the "drawer mechanism", and describes the realization of key technologies such as data transmission without interference , And finally gives a technical summary and outlook.

2. Overall system design

2.1 System structure characteristics

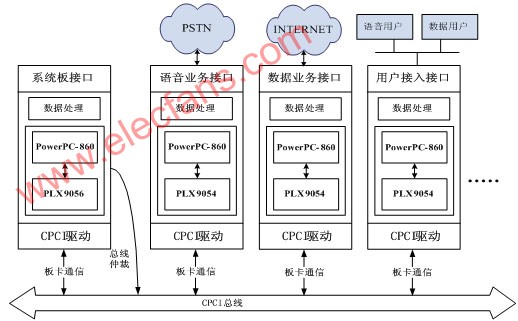

The structure of the distributed system we designed is shown in Figure 1. Different equipment boards in the system independently process the corresponding business data, convert it into unified IP data for interworking, and maintain their own routing tables to independently complete data forwarding. The system distributes the interface with a specific service network to various equipment boards for standard access channel adaptation, and distributes various network data to each board for processing and forwarding, achieving centralized configuration and distributed access Perfect combination with data processing.

In the CPCI distributed bus architecture, the backplane provides physical connection and circuit guarantee for bus exchange, and the system slot on the backplane provides bus arbitration, clock distribution, and restart of each card on the backplane; peripheral slots can be placed Simple interface board, intelligent slave device or bus control device [2,3]. Each CPCI board has a processor and an embedded real-time system. The processor uses Motorola ’s PowerPC-860 and PLX ’s 9054 and 9056 PCI bridge chips to establish an efficient and stable transmission between the PowerPC-860 and the CPCI bus. bridge. The PLX 9054/9056 chip implements the functions of the CPCI main control device, supports the PCI2.2 protocol, simplifies the design of the connection to PowerPC, and has good compatibility. It is easy to expand into a 66MHz clock and a 64-bit PCI bus, especially in PLX 9056 The embedded bus arbiter can reduce the system scale and make the system more stable [5].

Figure 1 Structure diagram of data communication system

2.2 System resource sharing and information exchange

The system adopts a distributed architecture of single bus multi-processor / multi-operating system based on CPCI. Each board in the system has an independent CPU and operating system, address and memory space, and independent I / O and interrupts, which can be completed independently. For data operation, each board can be regarded as a computer host. The topology formed by the distributed system is a fully connected network, each node in the network can directly access other nodes; from the perspective of CPCI bus transmission, all the cards on the slots are equal and can act as The master actively initiates the bus transmission. For this bus-based distributed architecture, we designed a cross-bus memory access mechanism to map the system memory or device memory (such as memory expansion cards) of other boards in the system to the local address space, and then use the same as the system memory Access the mapped memory in such a way that each board can access the memory resources of other boards on the bus.

2.3 Unified standardized access interface

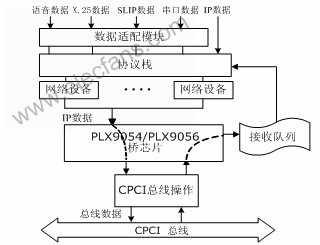

Heterogeneous networks are connected to distributed systems through standard channel adaptation. Voice, X.25, serial port data and other non-IP data are converted into IP data through the data adaptation module. The embedded real-time system of each board in the system processes the data And interaction. Various heterogeneous networks are connected to the corresponding network devices in the embedded system, and the network device driver calls the unified interface provided by the CPCI bus driver to realize the data transmission between the real-time system and the bus. When sending data, the network device driver uses the bus driver to control the bridge chip to perform address conversion, data forwarding, and interrupt generation, and generates corresponding bus operations to send data to the bus; when receiving data, the bus driver responds to the interrupt and receives the corresponding address on the bus Segment data, data analysis, address conversion, data forwarding, other interrupt generation and other operations in the interrupt service program. We use the Linux operating system, and its network system is mainly based on the UNIX socket mechanism. The system protocol stack and the driver transfer data through a special data structure (sk_buff). The data transmission process between the real-time system kernel and the CPCI bus is shown in Figure 2:

Figure 2 Flow chart of data transmission

3. Key technologies

3.1 "Drawer mechanism" for message storage

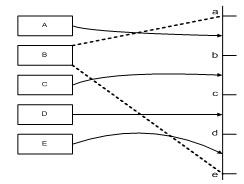

Each board in the system shares a CPCI bus. We propose a message storage strategy based on the "drawer mechanism" to ensure the interference-free transmission of data between boards. During the initialization phase when the board is added to the system, the system board allocates an independent PCI bus address range for each board on the bus, and writes the data to the designated address area when other boards send data to it. One board will receive data from different boards. In order to avoid the interference caused by each board sending data to the same base address, independent read and write space of the same size is allocated to other boards in the same board address area. It is named "Drawer". In this way, the data from a certain board will be sent to its corresponding "drawer", and each time the data is stored sequentially instead of overwritten to ensure the processing time of the board data. When the data length exceeds the remaining space of the drawer, it looks like a ring-shaped buffer is stored from the beginning. The "drawer mechanism" is shown in Figure 3. The square on the left represents different boards on the bus, and the right is the PCI bus address space. The corresponding address range of board B is from point a to point e, where the space between points ab is only used for data transfer from board A to B, and the space between points bc is only used for data transfer from board C to B. analogy.

Figure 3 "Drawer" for board data reception

Based on this message storage mechanism, we define several address tables to maintain address information related to data transmission. A static base address table is maintained on the system board, which records the pre-assigned base address for each card on the card slot. The board address map and transmission address offset table are maintained on all boards. The board address mapping table is an array of structures. Each item in the array represents a card slot, which contains address information such as card name, card slot number, base address, and address range for data transmission configuration. The data structure is as follows :

typedef struct _BUS_ADDR_MAPPING_INFO {

char board_name [BOARD_NAME_LENGTH];

int slot_number;

unsigned long base_addr;

unsigned long range;

ï½ BUS_AddrMapping_Info, * P_BUS_AddrMapping_Info;

The transmission address offset table is an unsigned integer array used to record the address offset of each board during data transmission between boards. The initial value is zero. Each time the transmission is completed, the address offset of the receiving board increases When the length of the secondary data transmission is insufficient to store the data to be transmitted, the offset address is set to zero and the data is written from the beginning of the area again. The data structure is defined as follows:

u32 current_offset_table [NUM_OF_SLOT] = {0, 0, 0, 0, 0, 0, 0, 0};

3.2 Data transmission

We have defined a data structure IPH (Internal Packet Header), which includes data type, length, source card slot number and other attributes. Before transmitting data, the packet is encapsulated as a header so that the receiver can analyze the packet header according to the data service type. Differentiate. The main IPH types are board configuration information, port registration information, routing information, and unknown data types. Define the data structure iph_attr distinguishes different IPH_info types, located at the head of the data packet, and its data structure is as follows:

typedef struct _IPH_ATTR {

u32 board_id; / * from which board * /

int iph_type; / * datagram type * /

unsigned long length; / * datagram length (without IPH) * /

ï½ IPH_ATTR, * P_IPH_ATTR;

Different data structures are defined separately for various types of IPH information, which are sequentially stored in the data packet header after the iph_attr structure.

When sending data, IPH encapsulate the data, select the destination PCI address according to the aforementioned board card address mapping table, and then call the bus interface function to complete the data transmission. The sender notifies the receiver of the transmission address and data length by writing the mailbox register of the receiving board bridge chip, and generates an interrupt to trigger reception. The PLX bridge chip supports direct access of the local bus to the PCI bus. It has 8 mailbox registers. The first four can generate interrupts. Each mailbox has 32 bits. The transmission address and data length information use mailbox i and mailbox i + 4 to work together. In this way, when the receiver receives two parameters, it will generate an interrupt to receive the data [5]. This mechanism enables the reception process to have four service windows, which improves system throughput.

The mailbox that receives the PLX chip of the board is written with parameters to generate a local interrupt check "drawer". Before the interrupt is generated, the data has actually been sent to the target board. The interrupt service program maintains a data queue for the receiving end, it reads the information in the mailbox, analyzes the address to find the corresponding data and submits it to the bottom half for processing. The bottom half parses the IPH of the data packet to distinguish the data type. If it is configuration, port, routing and other information, it will be configured accordingly. If it is data information, it will be processed or forwarded.

In summary, the system completes the mapping of the PCI address space between each board through the "drawer mechanism" and the maintenance of several address tables. The board writes the data to the mapped address space and can transfer the data to the target through the bus. On the board, it realizes the cross-bus memory access of the board; customize the IPH data header to distinguish the data type to assist the data information management, complete the routing maintenance, and the logical function of the forwarding engine, realize the interference-free transmission of data and effective communication management .

4. Summary and outlook

The author's innovation in this article is: A distributed system design based on CPCI is presented, and a message storage mechanism and address information maintenance strategy based on the "drawer mechanism" are also proposed. The distributed system based on CPCI described in the article can achieve 64bit bus width and 264MB / s peak bandwidth. Each host in the system can independently complete data processing and communication, and can carry multiple services of voice and data. The access board is connected to the PSTN network connected to the voice service board and the Internet connected to the data service board for data communication, and has great application prospects in the fields of communication and military affairs. In order to make this communication system more practical on a large scale, future work includes:

(1) Implement a set of easy-to-operate remote management system in order to complete the monitoring and deployment of communication services;

(2) Design CPCI interface boards that support more business types, such as xDSL, H.264, etc .;

(3) In the case of large external interference, strict performance tests are performed to prove that the system can meet the carrier-class business requirements.

Heated Eye Mask,Self Warming Eye Mask,Steam Eye Mask,Warm Compress Eye Mask

Ningbo Sinco Industrial & Trading Co., Ltd. , https://www.newsinco.com