About 40 years ago, Comprehensive CompuTIng Systems and Services introduced the first commercial digital software simulator called TEGAS on the market, which is used primarily for test generation and software simulation systems. This system for simulating gate-level circuits was developed by a small team of experts, and previously only simulation software was developed for transistor-level circuits. TEGAS is its dedicated description language. This language is only used to generate digital circuit test vectors. Ultimately, design verification is still required through the prototype board.

With the rise of the Computer Aided Engineering (CAE) industry in the early 1980s, digital software simulators or logic software simulations became popular in the electronic engineering community and became the primary means of design verification. By the end of the 1990s, digital software simulators evolved into register transfer level (RTL) software simulators that supported two popular hardware description languages ​​(HDLs), Verilog and VHDL. Existing EDA (Electronic Design Automation, a product of CAE and CAD) has been commercially available for more than a decade to support both languages ​​in the same tool. Today, three major EDA vendors, Synopsys, Cadence and Mentor Graphics, offer their own HDL software simulators, which are in a three-pronged state on the market.

A series of improvements over the years have made the HDL software simulator even more perfect. It is now an infinite tool and an indispensable tool in design verification and what-if analysis, but it has its own limitations, that is, the design scale cannot exceed 100 million ASIC equivalent gates. This limitation is more casual. In fact, software simulations can still be performed on larger designs, but the execution speed is extremely slow.

An example

To simulate a one-second real data on a 100 million ASIC gate design running at 100 MHz using a modern software simulator running at 10 Hz, this is no easy task. In this design complexity, it may take 10 million seconds. That is 2,778 hours, or 115 days. One second of 100 MHz real data equals 100 million clock cycles, which is quite large and may exceed the requirements of a typical test platform. One millisecond or less is sufficient when dealing with a typical test platform, and when running on the latest PC with a large memory configuration, the execution time is reduced to one day or less. This is a reasonable goal.

HDL software simulators can run in parallel in a PC farm, and each PC handles a fully functional test platform. The semiconductor company has a computing field of tens of thousands of PCs running all day.

But 100 million cycles are still not enough to handle embedded software design. Since the processing software is essentially a serial process, it is necessary for this task to execute billions of cycles in sequence. However, PC farms with HDL software emulation licenses are beyond the reach. Software programs cannot be split in a subset and run in parallel.

So how do you verify the embedded software designed by SoC?

Enter the era of hardware simulation

Hardware simulation has been around for a long time, and it gives designers a more accurate description of circuit behavior before streaming, because hardware simulation is implemented through real circuits and logic. Hardware simulation began in the late 1980s and was popular in the late 1990s, primarily through commercial FPGAs to validate processors and graphics designs that required longer test cycles. They also encounter various problems such as high difficulty in circuit modeling and low reliability. The cost is also relatively high, and as a single-user resource, its return on investment is low. However, the excellent execution speed of the hardware emulator still makes it a necessary tool for long processing cycles.

As in the previous example, a hardware emulator running at 1 MHz would take 100 seconds to execute 1 second of real data and process 100 million cycles. The hardware emulator can boot the operating system in an hour or so. Moreover, the investment in hardware emulators is much cheaper than re-spinning.

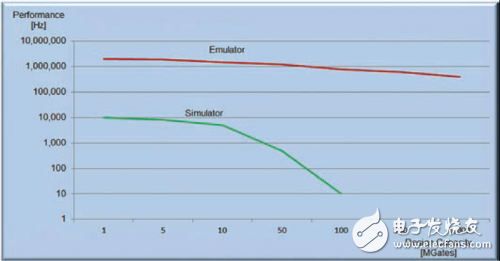

Figure 1: Comparison of software simulation and hardware simulation performance at different design scales.

Due to cache misses and memory swaps, HDL software emulators slow down as the design scale increases. However, in this case, the performance of the hardware emulator will only be slightly affected (see Figure 1).

Due to the limitations of commercial FPGA hardware emulators, custom chip hardware emulators have emerged. There are two main types of hardware emulators: custom FPGA hardware emulators from Mentor Graphics, also known as on-chip hardware emulators; and processor-based hardware emulators from Cadence Design Systems. Synopsys also supports the latest commercial FPGA hardware emulators that are more advanced and enhanced than standard FPGA hardware emulators.

Until a decade ago, hardware emulators were separately deployed as physical test environments in Circuit Hardware Emulation (ICE) mode. The design under test (DUT) will eventually reside in this environment as the tape provides stimulus and processing response. Because it's difficult to set up, ICE mode is not common now, and the need for a more flexible test environment is growing. Application hardware bridges have no controllability/reproducibility, and they increase the complexity of the test environment due to increased installation time and maintenance costs. Since the synthesizable testbench can be mapped inside the hardware emulator and can be executed at the highest speed of the hardware emulator without relying on the external environment, there are other viable alternatives to the testbench area. Unfortunately, they are not easy to develop.

Transaction-based verification or acceleration (TBV or TBX) is the industry's most optimistic approach and has two advantages. First, it's easy and error-free to write a test platform at a higher level of abstraction with an order of magnitude less code. Second, these test platforms perform faster than traditional RTL platforms due to the dramatic acceleration of the bus function model (BFM) that maps transistors inside the hardware emulator. Another benefit is that the TBV or TBX does not require human supervision to handle the speed adapter when the user switches designs or new user logins. This approach is also suitable for remote access.

When to use software emulation, when to use hardware emulation

The HDL software simulator is suitable for hardware debugging in the early stages of the design cycle, and the early stages of design are primarily focused on the module level. They are extremely flexible in debugging hardware design due to their ease of use, quick setup, and extremely fast design compilation. They also support multiple design iterations every day... as long as the design is reasonably sized. But there are problems at tens of millions of levels, which is now typical of system-level design verification. As mentioned above, they are not suitable for embedded software verification.

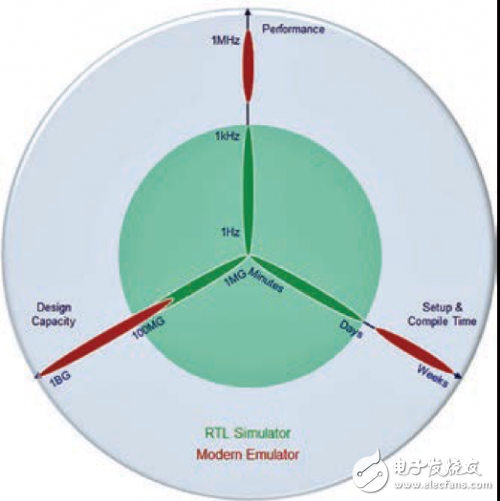

In contrast, hardware emulation can find almost all design flaws, whether in hardware or in SoC embedded software. Hardware emulation can handle any design size, but it takes a long time to build the environment, at least one day, or longer. Moreover, compared to software emulators, the compilation speed is relatively slow, and it takes about an hour to complete the compilation (see Figure 2).

Figure 2: Software simulation vs. hardware simulation based on performance, design capabilities, and setup/compile time.

Modern hardware emulators support multiple concurrent users, including remote access, thus increasing return on investment.

Solar Street Light is powered by crystal silicon solar cell,maintenance-free calve controlled sealed battery to store electricity,ultra-bright LED lamap as the light source,and controlled by intelligent charge and discharge controller,used to replace the tradional public electric lighting street light.

No need to lay cables,no need for ac power supply,no electricity charges; DC power supply,photosensitive control; solar street light has the advantages of good stability,long life,high lumious eeficiency,easy installation and maintenance,high safety performanc,energy conservation and environmental protection,economic and practical.

Solar Street Light

Solar Street Light,Solar Street Lamp,Smart Street Light,Solar Powered Street Lights

Jilin Province Wanhe light Co.,Ltd , https://www.wanhelight.com